ホーム > 要素技術

- ベースボード動作保証速度200MHz以上

- 10GHz以上の高速シリアル通信技術

- HD-SDI (1.485Gbps)の入出力動作実績

- 画像・映像系システムの提供が豊富

- 仕様書からの作成能力

- 数学モデルから回路設計、基板、実装まで

- 大規模FPGA高速動作設計

- 高速メモリ設計(DDR2、DDR3)

- 高速シリアル伝送プロトコル(HD-SDI、LVDS、DVI、Camera Link、USBなど)

- 高速デジタル・アナログ混載システム

- GHz帯プリント配線基板設計

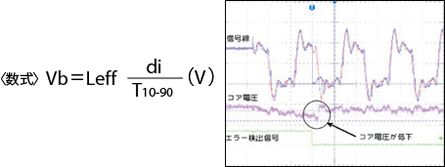

バウンスによる内部回路誤動作の様子

66MHz,512bit全ピンをトグルさせた瞬間にコア電圧が下がり、内部回路が誤動作した様子を捉えた波形。電源電圧の変位がわかります。周期的な変位ではないので、誘導ではなくバウンスが原因です。

アキュベリノスシリーズは機能モジュールごとに高速大容量電源モジュールが用意されており電圧低下による動作不具合を極力少なくします。

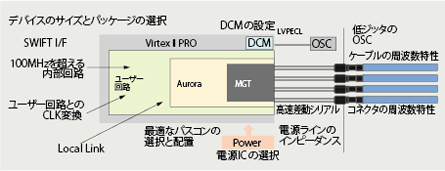

高速動作を実現する構成要素

高速シリアルインタフェースとして使用するには様々なノウハウが必要です。

アキュベリノスシリーズには電源、パスコン、高速インタフェースなどを安定に稼動させる環境が整っています。

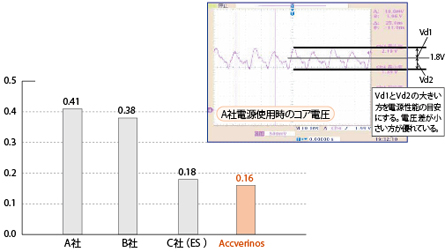

使用FPGAに適合した電源回路を開発

クリアランス、層構成対策を施したプロトタイプで、66MHz、256bit全ピンをトグルさせた場合の最大出力電圧変動値。

アキュベリノスシリーズは負荷電流が過渡的に変化した時でも、安定した電圧を保ちます。電圧は高速になるほど不安定になるので、電圧を安定させる回路は高速検証には必須の技術です。

インピーダンスを考慮したプリント基板設計

基板上の僅かな設計の差が、回路全体のインピーダンスを大きく左右します。

アキュベリノスシリーズは回路特性の障害になるスルーホールの形状、位置などのインピーダンスを考慮した基板設計をしています。